SuperCISC Fabric

PIs: Alex K. Jones, Brady Hunsaker

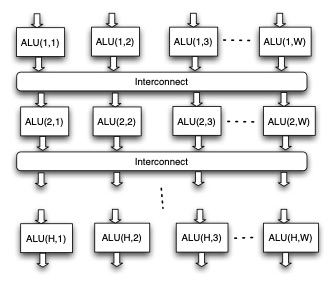

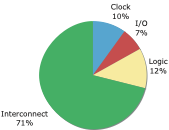

Embedded applications, image and signal processing algorithms in particular, are predominantly implemented using one of two methods, execution on an embedded processor or fabrication of an Application Specific Integrated Circuit (ASIC) the former for ease of development and verification and the latter for high-performance and/or low-energy implementation. However, there is a large design space between these two techniques that continues to change under three (3) often contradictory trends for embedded systems: changes in fabrication technology, new application demands, and increasing productivity pressures on designers. The Field Programmable Gate Array (FPGA) has attempted to create a middle ground between performance and productivity. Deficiencies in this solution have limited its success for this design space. For example, unlike embedded processors, the FPGA requires Computer-Aided Design (CAD) tools that work at the gate level and unlike ASICs it has a poor power efficiency.

The SuperCISC fabric solves these limitations inherent in FPGAs and provides an appropriate high-performance and energy-efficient hardware solution with the programmability of an embedded CPU. By considering an integrated approach that includes research in both architecture design through the development of a low-power high-performance reconfigurable fabric and tool development by creating an automated C to bit-stream compilation and CAD flow, SuperCISC will exploit many opportunities for power and performance optimization that standalone tools or architectures cannot.

This project is funded by the Technology Collaborative (TTC) advised by Seagate, Ericsson, Novocell Semiconductor, Concurrent EDA, and ADCUS.

Related Publications

-

•C. Ihrig, M. Baz, J. Stander, R. R. Hoare, B. A. Norman, O. Prokopyev, B. Hunsaker, and A. K. Jones, “Greedy Algorithms for Mapping onto a Coarse-grained Reconfigurable Fabric,” Invited Book Chapter in Advances in Greedy Algorithms, V. Kordic, editor, I-Tech Education and Publishing, Vienna, Austria, October 2008.

-

•G. Mehta, C. Ihrig, and A. K. Jones, “Reducing Energy by Exploring Heterogeneity in a Coarse-grain Fabric,” in Proc. of the Reconfigurable Architecture Workshop (RAW), 2008

-

•A. K. Jones, G. Mehta, J. Stander, M. Baz, and B. Hunsaker, “Interconnect Customization for a Hardware Fabric,” ACM Transactions on Design Automation for Electronic Systems (TODAES) - accepted for publication.

-

-

•A. K. Jones, R. Hoare, D. Kusic, G. Mehta, J. Fazekas, and J. Foster, Reducing Power while Increasing Performance with SuperCISC, ACM Transactions on Embedded Computing Systems (TECS) - Vol. 5, No.3, August 2006, pp. 658-686.

-

•G. Mehta, R. R. Hoare, J. Stander, J. Lucas, B. Hunsaker, and A. K. Jones, A Low-Energy Reconfigurable Fabric for the SuperCISC Architecture, Journal of Low Power Electronics (JOLPE) - Vol. 2, No. 2, August 2006, pp. 148-164.

-

•G. Mehta, J. Stander, M. Baz, B. Hunsaker, A. K. Jones, Interconnect Customization for a Coarse-grained Reconfigurable Fabric, in Proc. of the IPDPS Reconfigurable Architecture Workshop (RAW), 2007.

-

-

•G. Mehta, R. Hoare, J. Stander, A. K. Jones, A Low-Energy Reconfigurable Fabric for the SuperCISC Architecture, in Proc. of the IEEE Symposium on Field Programmable and Custom Computing Machines (FCCM), 2006.

-

-

•G. Mehta, R. Hoare, J. Stander, A. Jones, Design Space Exploration for Low-Power Reconfigurable Fabrics, in Proc. of IEEE/ACM Reconfigurable Architectures Workshop (RAW), 2006.

•A. K. Jones, R. Hoare, D. Kusic, J. Fazekas, G. Mehta, and J. Foster, A VLIW Processor with Hardware Functions: Increasing Performance While Reducing Power, IEEE Transactions on Circuits and Systems II, Vol. 53, No. 11, November 2006, pp. 1250-1254.

•R. Hoare, A. K. Jones, D. Kusic, J. Fazekas, J. Foster, S. Tung, M. McCloud, Rapid VLIW Processor Customization For Signal Processing Applications Using Combinational Hardware Functions, EURASIP Journal on Applied Signal Processing (JASP), Vol. 2006, Article ID 46473, 2006, pp. 1-23.

•A. K. Jones, R. Hoare, D. Kusic, J. Fazekas, and J. Foster, An FPGA-based VLIW Processor with Custom Hardware Execution, in Proc. of the ACM International Symposium on Field-Programmable Gate Arrays (FPGA) 2005, pp. 107-117.

•D. Kusic, R. Hoare, A. K. Jones, J. Fazekas, J. Foster, Extracting Speedup from C-code with Poor Instruction-level Parallelism, in Proc. of the IPDPS Workshop of Massively Parallel Processing (WMPP), 2005, pp. 264-9 - 264-18.

Fabric Architecture

FPGA Power Breakdown

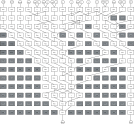

Mapped ADPCM Decoder